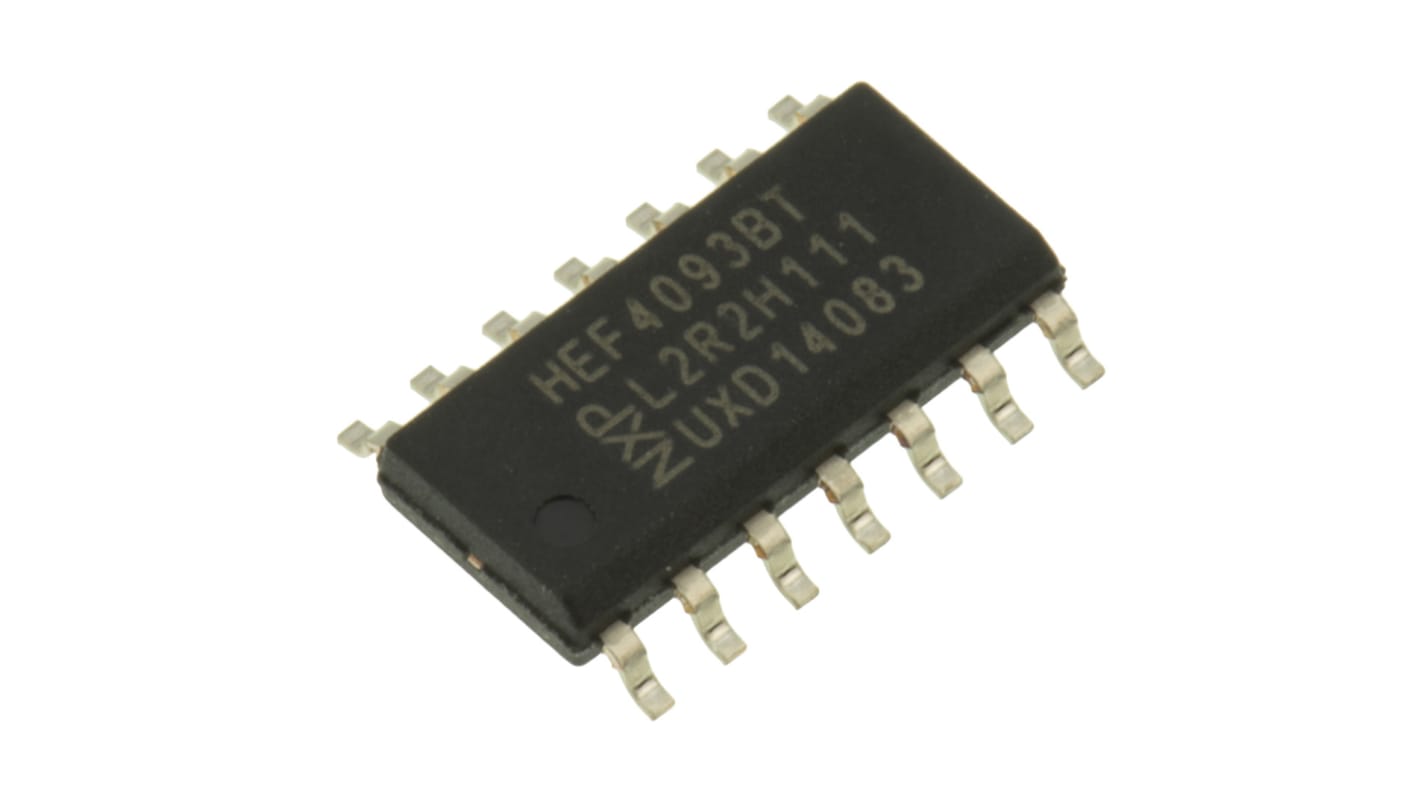

Nexperia HEF4093BT,652, 4 2-Input NAND Schmitt Trigger Input Logic Gate, 14-Pin SOIC

- RS Stock No.:

- 124-2313

- หมายเลขชิ้นส่วนของผู้ผลิต / Mfr. Part No.:

- HEF4093BT,652

- ผู้ผลิต:

- Nexperia

รูปภาพประกอบสินค้าเป็นเพียงรูปภาพใกล้เคียงเท่านั้น กรุณาอ่านรายละเอียดสินค้า

ยอดรวมย่อย (1 หลอด หลอดละ 57 ชิ้น)*

THB312.189

(ไม่รวมภาษีมูลค่าเพิ่ม)

THB334.02

(รวมภาษีมูลค่าเพิ่ม)

ส่งฟรีหากซื้อเกิน ฿2,500.00

สต็อกสุดท้ายของ RS

- เพิ่มอีก 2,166 ชิ้นจะส่งได้หลังจากวันที่ 11 พฤษภาคม 2569 ไปอีกประมาณ 7 วันทำการ

- 9,633 ชิ้นสุดท้ายส่งจากวันที่ 18 พฤษภาคม 2569

ชิ้น | ต่อหน่วย | ต่อหลอด* |

|---|---|---|

| 57 + | THB5.477 | THB312.19 |

*ตัวบ่งบอกราคา / price indicative

- RS Stock No.:

- 124-2313

- หมายเลขชิ้นส่วนของผู้ผลิต / Mfr. Part No.:

- HEF4093BT,652

- ผู้ผลิต:

- Nexperia

คุณสมบัติ / Specifications

ข้อมูลทางเทคนิค / Technical Data Sheets

Legislation and Compliance

รายละเอียดสินค้า / Product Details

ค้นหาผลิตภัณฑ์ที่คล้ายกันโดยเลือกคุณลักษณะอย่างน้อยหนึ่งรายการ

เลือกทั้งหมด | คุณลักษณะ | ค่า |

|---|---|---|

| Brand | Nexperia | |

| Logic Function | NAND | |

| Product Type | Logic Gate | |

| Mount Type | Surface | |

| Number of Elements | 4 | |

| Number of Inputs per Gate | 2 | |

| Schmitt Trigger Input | Yes | |

| Package Type | SOIC | |

| Pin Count | 14 | |

| Logic Family | 4000 | |

| Input Type | Schmitt Trigger | |

| Maximum High Level Output Current | -4.2mA | |

| Minimum Operating Temperature | -40°C | |

| Maximum Propagation Delay Time @ CL | 185ns | |

| Maximum Operating Temperature | 125°C | |

| Minimum Supply Voltage | 3V | |

| Height | 1.45mm | |

| Length | 8.75mm | |

| Series | HEF4093B | |

| Standards/Approvals | JEDEC JESD 13-B | |

| Maximum Supply Voltage | 15V | |

| Maximum Low Level Output Current | 4.2mA | |

| Automotive Standard | No | |

| เลือกทั้งหมด | ||

|---|---|---|

Brand Nexperia | ||

Logic Function NAND | ||

Product Type Logic Gate | ||

Mount Type Surface | ||

Number of Elements 4 | ||

Number of Inputs per Gate 2 | ||

Schmitt Trigger Input Yes | ||

Package Type SOIC | ||

Pin Count 14 | ||

Logic Family 4000 | ||

Input Type Schmitt Trigger | ||

Maximum High Level Output Current -4.2mA | ||

Minimum Operating Temperature -40°C | ||

Maximum Propagation Delay Time @ CL 185ns | ||

Maximum Operating Temperature 125°C | ||

Minimum Supply Voltage 3V | ||

Height 1.45mm | ||

Length 8.75mm | ||

Series HEF4093B | ||

Standards/Approvals JEDEC JESD 13-B | ||

Maximum Supply Voltage 15V | ||

Maximum Low Level Output Current 4.2mA | ||

Automotive Standard No | ||

- COO (Country of Origin):

- TH

The HEF4093B is a quad two-input NAND gate. Each input has a Schmitt trigger circuit. The gate switches at different points for positive-going and negative-going signals. The difference between the positive voltage (VT+) and the negative voltage (VT-) is defined as hysteresis voltage (VH). It operates over a recommended VDD power supply range of 3 V to 15 V referenced to VSS (usually ground). Unused inputs must be connected to VDD, VSS, or another input.

Key features and benefits

Mixed 5 V and 3.3 V applications

Reduce time to market for complex designs

Save board space

Open-drain output options

Improved signal integrity for complex layouts

Wide supply voltage range

Low propagation delay

Overvoltage tolerant options

Low input threshold options

CMOS low power

ลิงก์ที่เกี่ยวข้อง

- Nexperia HEF4093BT 4 2-Input NAND Schmitt Trigger Input Logic Gate, 14-Pin SO

- Nexperia 74HCT132D 4 2-Input NAND Schmitt Trigger Input Logic Gate, 14-Pin SOIC

- onsemi 14-Pin SOIC

- Texas Instruments CD4093BF 14-Pin CDIP

- DiodesZetex 14-Pin TSSOP

- DiodesZetex 74HCT00S14-13 14-Pin SOIC

- onsemi MC14093BDR2G 14-Pin SOIC

- onsemi MC14093BDG 14-Pin SOIC